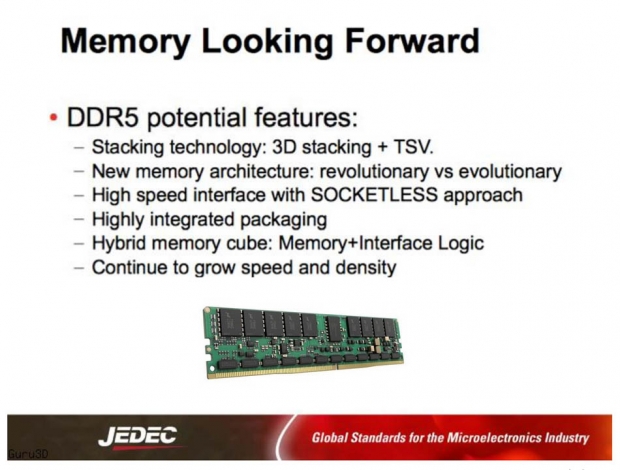

DDR5 to use 3D chip stacking with TSVs

As with any new forecasted memory standard, the association says that DDR5 (Double Data Rate 5) memory will offer improved performance with greater power efficiency as compared to previous generation DRAM technologies. DDR5 will provide double the bandwidth and density of DDR4 along with improved channel efficiency, making it ideal for high performance combined with improved power management and cost savings.

DDR5 is expected to become the industry’s first DIMM approach that will include 3D chip stacking using through-silicon vias (TSVs), similar to what Toshiba has been doing with NAND flash since 2015. Since TSVs can be placed anywhere on the chip rather than just at the edge, it's easy to implement a wide data bus with higher performance and low-power through shorter distances.

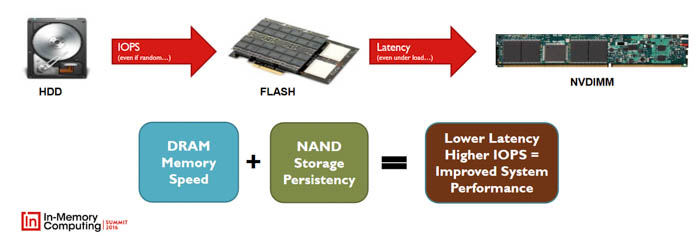

NVDIMM-P: Combining NVM or NAND flash with DRAM memory space

Mian Quddus, Chairman of the JEDEC Board of Directors, said that increasing server performance requirements are driving the need for more advanced technologies, and the standardization of next generation memory such as DDR5 and the new generation persistent modules NVDIMM-P will be essential to fulfilling those needs.

The organization has announced that it is also working on a standard for non-volatile hybrid memory called NVDIMM-P, or “Non-Volatile Dual Inline Memory, Persistent,” that basically would map DRAM and NAND to the same memory space. The proposed standard effectively provides both byte- and block-level drive access.

Source: In-Memory Computing Summit 2016

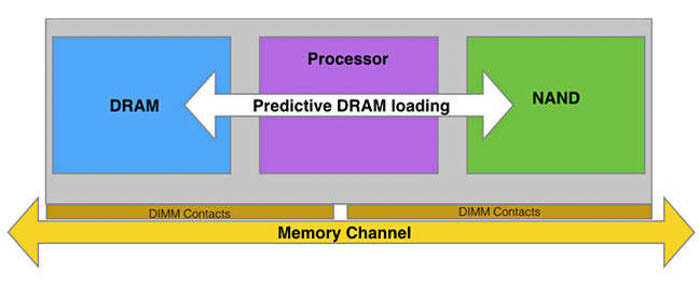

According to JEDEC task group leader Jonathan Hinkle, there are three different types of non-volatile DIMMs, which include NVDIMM-N, NVDIMM-F, and NVDIMM-P. The first type uses only onboard Flash memory to save DRAM contents after a crash or power failure. The second type is for all-flash DIMMs, or NAND-based modules such as Diablo’s Memory 1 and SanDisk ULLtra DIMMs, that are byte-addressable and more economical than conventional DRAM. The third and latest type will probably have the speed of traditional DRAM, but may be somewhat slower as it includes capacity from NVM or NAND flash modules. All NVDIMM modules are expected to deliver the absolute lowest latency available to a server as they do not require I/O or even DMA, all without the operating system yielding interference between applications and modules.

Generic NVDIMM-P

Latency for NPDIMM-P is expected to be in the 100s of nanoseconds and will support both existing DDR4 and upcoming DDR5 protocols, with capacity in the hundreds of gigabytes to lower terabytes range. The modules will appear as disk drives to applications and will be pooled together to create storage spaces. The JEDEC group expects NVDIMM modules to be highly adopted for analytics and machine learning applications, databases and in-memory workloads, persistent memory file systems, and metadata log acceleration.

More details from JEDEC later this year

JEDEC plans to host in-depth technical workshops on both DDR5 and NVDIMM-P to provide customers and end-users with a better understanding of these standards and promote their industry-wide adoption in 2018. More details on both standards will be available on the JEDEC website later this year.