Intel and many other companies in the semiconductor industry made a big deal about Foveros 3D packaging, but Victor informed the audience at the post-XDF Europe keynote that Xilinx has been using 3D packaging since its 28nm products. It sounds like the company has been doing 3D packaging for more than a decade without making a big splashy noise about it.

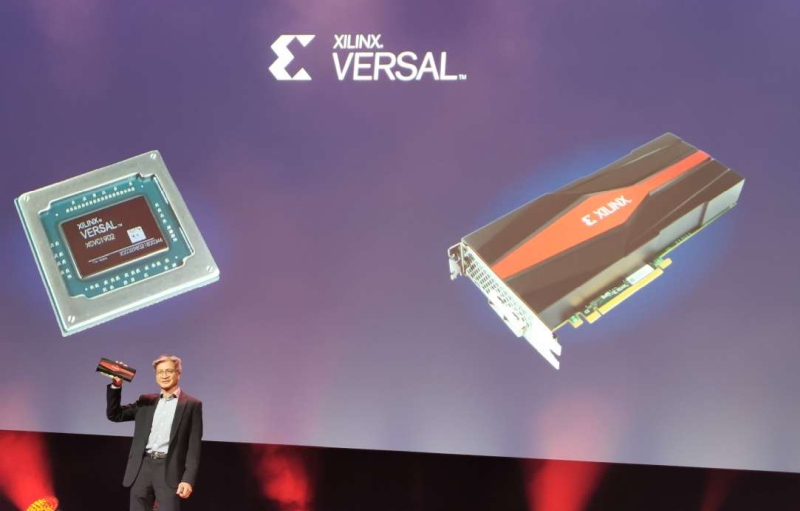

The Versal today is monolithic, but some other products will be based on chiplet and multi-chip approach. The industry needs bigger SoCs and processing accelerators, and doing a chiplet model gives a better yield. It is easier to make a smaller die than a larger due to the concern that something can go wrong on a big die.

The market is comparing Versal solutions versus GPU which are being deployed on the AI and machine learning level. Latency is where Xilinx dominates, and even toughest science products as Cern research uses FPGA for its adaptability and programmability and still get 3nm latency levels. A CPU on the same system looking for Higgs Boson has a latency of 100ns.

Victor also mentioned that TSMC would not be at the level with 3D packaging where they are today without help from Xilinx. The company contributed to some very popular memory technologies, including HBM 2, with AMD and came up with some innovative and unique approaches.

The 3D chip packaging can help companies like Intel get to a very dens design wins and small spaces, but it can also enable the faster chip to chip communication at fast, close to the chip interconnect.

The last thing that the President and CEO of Xilinx mentioned that there would be bigger Versal multi-chips coming in the future.