Victor Peng announced the Versal platform, calling it industry’s first adaptive compute acceleration platform (ACAP). The ACAP got a lot of attention as it is a 7nm, so leading-edge chip, and it is very programmable in both hardware and software.

The general idea behind the Versal platform is the fact that a programmable hardware approach, the FPGA can solve some problems better than the traditional CPU, GPU or ASICs approach. These three categories deal with fixed function hardware that cannot be updated while the FPGA programmable hardware approach.

This is how Xilinx came up with ACAP adaptive compute acceleration platform offering heterogeneous acceleration for any developer and addressing any application.

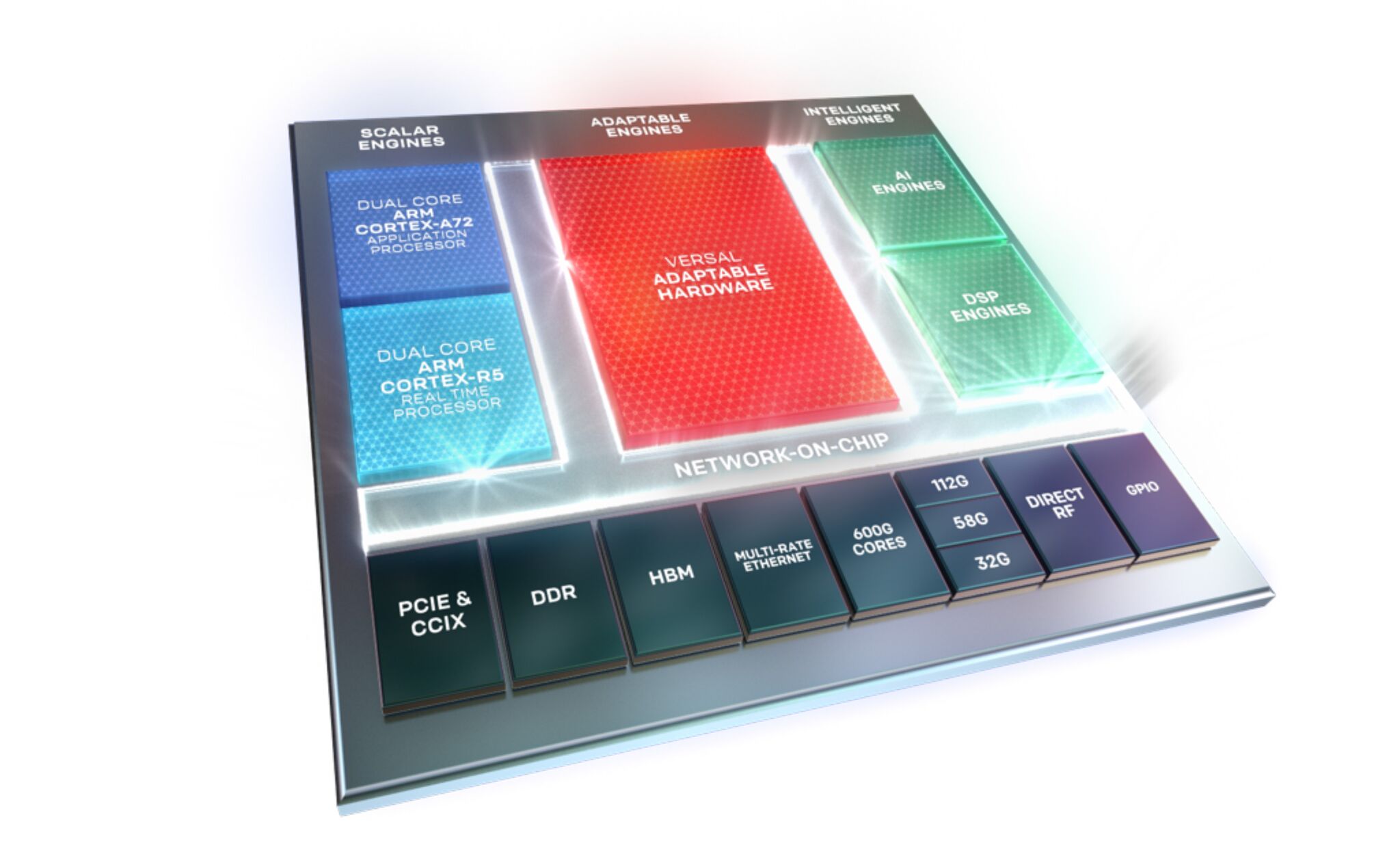

Kirk Saban SR direction of product and technical marketing, has spent some time going into details explaining the building blocks inside of the Versal APAC. The unique programmable chip has a scalar processing engine, adaptable hardware engine, intelligent engine that are software programmable and hardware adaptable, advanced protocol engines and the incredible stack of I/O.

Building programmable blocks

The scalar processor uses two Cortex A72 for application processing due to its ECC ability that industries like automotive absolute insist upon. The Versal has two Cortex R5 real time processors for real time mission critical tasks as well as platform management controller.

Adaptable hardware engines have been re-architectured with a foundational hardware fabric designed for 7nm great compute density. It enables custom memory hierarchy and 8X faster dynamic reconfiguration on the fly.

The intelligent engine part of the chip includes the DSP engine with high precision floating point and low latency granular control for customized data paths as well as AI Engines for high throughput, low latency and power efficient part of the chip that is ideal for AI inference and advanced signal processing.

The i/O part has the Gen 4 PCIe 16X, integrated AXI DMA and CCIX for seamless acceleration of server class CPUs. The memory controllers support DDR4 3200, LPDDR4 4266 and High bandwidth memory aka HBM. Integrated protocol engines include 100G multirate Ethernet, 600G Ethernet, and Interlaken as well as 600G Cryptographic engines (AES/IPSEC/MACSEC).

Versal supports a broad range of transceivers including 32G power optimized for edge applications, 58G PAM 4 in mainstream devices and 112G PAM 4 industry highest performance.

There is support for integrated RF signal chain including the next generation multi GSPS direct RF-ADC/DAC, Integrated DDC/DUC as well as SD-FEC for 5G and docsys. One can imagine that cable internet providers, as well as the 5G companies, will definitely want to have these featured supported.

Six different markets

The product portfolio includes six series of devices uniquely architected to deliver scalability and AI inference capabilities

for a host of applications across different markets, from cloud to networking, wireless communications, edge computing all the way to endpoints.

“With the explosion of AI and big data and the decline of Moore’s Law, the industry has reached a critical inflection point. Silicon design cycles can no longer keep up with the pace of innovation”, says Peng.

"Versal is the industry’s first ACAP. We uniquely designed it to enable all types of developers to accelerate their whole application with optimized hardware and software and to instantly adapt both to keep pace with rapidly evolving technology. It is exactly what the industry needs at the exact moment it needs it.”

Xilinx talked about the Versal AI and Versal Prime. The Versal AI addresses highest compute and lowest latency, enabling breakthrough AI inference throughput and performance. The series is optimized for cloud, networking, and autonomous technology, offering the highest range of AI and workload acceleration available in the industry.

The Versal Prime series is designed for broad applicability across multiple markets and is optimized for connectivity and in-line acceleration of a diverse set of workloads.

There is also a massive software stock that comes with the Versal platform and Xilinx is currently engaged with multiple key customers through its early access program.

The Versal Prime series and Versal AI Core series will be generally available in the second half of 2019. Stay tuned for much more details from the Xilinx XDF developers conference.