Things are on schedule to ship 7nm Versal later this year, and the solution represents the Swiss knife of heterogeneous computing, addressing some key markets including AI, cloud, network infrastructure, 5G, and automotive.

100 customers in early access

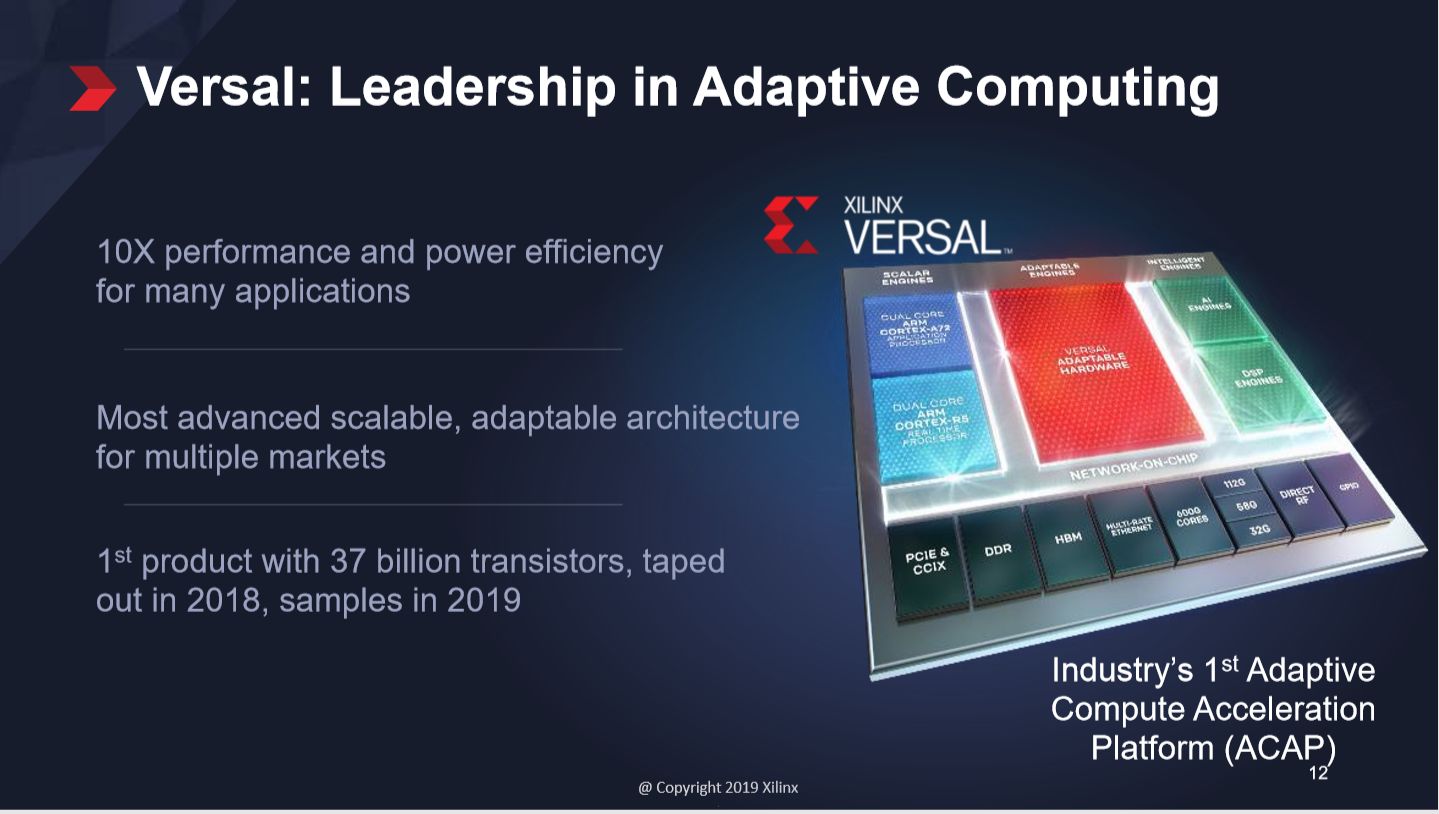

Versal, thanks to its adaptive nature, can address multiple growing markets and can adapt to the needs of specific workloads. Versal is the adaptive compute acceleration platform (ACAP) that got attention over 100 customers in the early access program. They are working on the tools and expecting to get silicon samples.

37 billion transistors and more

The Versal chip was taped out last year, and Victor mentioned that the company plans to sample the chips in 2019. Versal packs 37 billion transistors in its 7nm design, and the number itself promises a lot of computational power. Versal 7nm is a single monocytic chip and not chip packaging that became popular for chipset designs. Victor Peng reassured us that this is not the largest chip in the family.

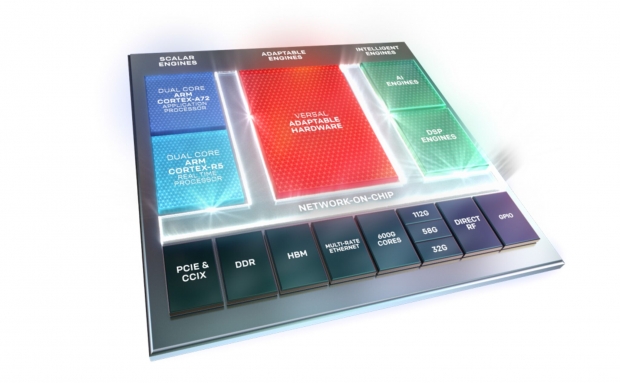

Versal enables 10X performance and power efficiency for many applications. The architectural design of the Versal chip is targeting the performance and power efficiency of modern applications, and on top of that, pipelines can adapt via programmable part of the chip. ACAP - the adaptive compute acceleration platform - is a new and innovative product in the AI and general data workload approach.

Versal built from the ground up

Versal is not an FPGA or the iteration of a Zynq product. Victor reminded us that the chip is based on the whole new architecture, including new AI engine optimized for multiple neural network acceleration as well as any linear algebra intense applications.

Victor calls Versal the most powerful comprehensive architecture Xilinx ever implemented, and it is scalable up for high performance or down for more cost and power sensitivity.

ACAP comes in six series expected over the next couple of years and intented to cover all the markets that Xilinx serves. Xilinx traditionally holds a Xilinx developer conference in early October, and we are sure that the company will be ready to talk more about it then.