US patent document concerns an "Instruction subset implementation for low power operation" and it was spotted by Underfox of Twitter and shared a link to the patent PDF.

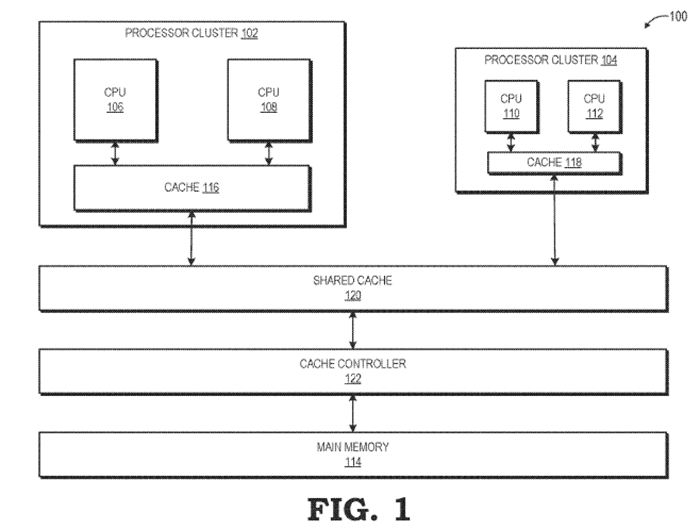

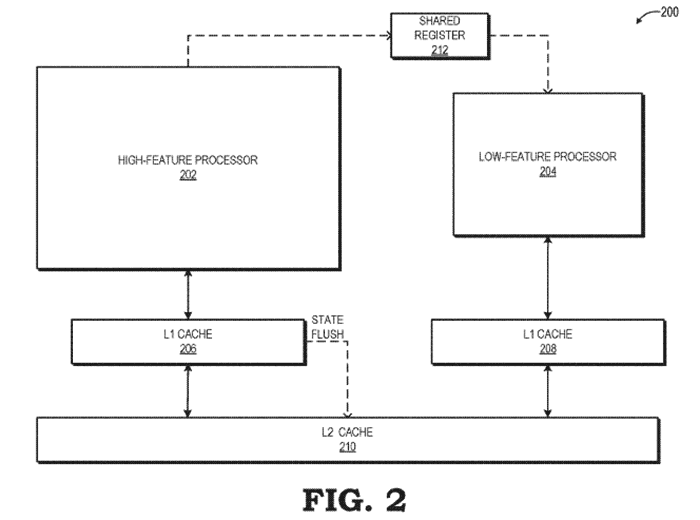

AMD appears to be building a heterogeneous processor which mixes full or "high-feature" CPU cores with "low-feature" CPU cores implementing a subset of ISA features. This appears to be an answer to ARM's 'big.LITTLE' project and has similarities to Intel's Lakefield hybrid architecture.

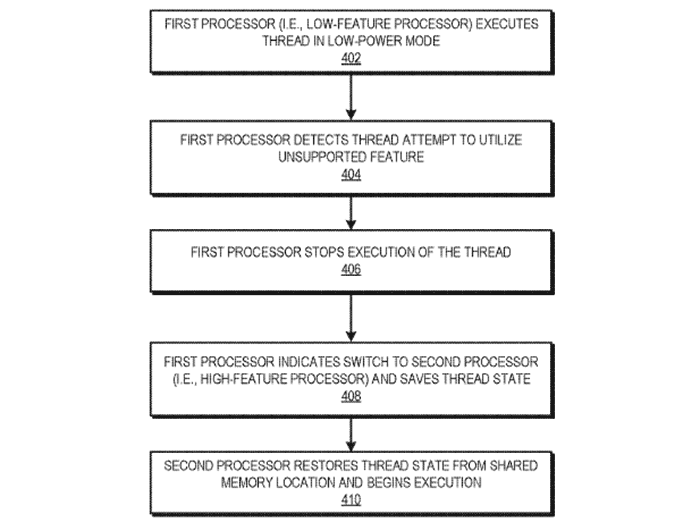

AMD's goal for hybrid architecture is power saving. The patent abstract said that the lower-feature second processor is configured to execute an instruction thread by consuming less power and with lower performance that the first processor.

In the proposed architecture, low-feature processor cores will be able to turn off high-feature processors when not being used. It is important that the low-feature cores have support for various low-priority processes that run frequently if not constantly - OS maintenance, timer support, monitoring functionality.

Figures are provided in the patent document. One shows how the low-and high-feature processor clusters with a shared cache, controller and main memory access. For communication between the core clusters there are several options available and illustrated in patent diagrams.