RISC-V could go the way of Arm and x86

Torvalds’ prophecy

The softly spoken Linux prophet, Linus Torvalds has been consulting his bones and concluded that RISC-V might fall into the same development chasm between hardware and software developers seen by Arm and x86.

Android heading towards RISC-V

Unless the US government, Arm and Intel can stop it

The Android ecosystem is moving toward a RISC-V future with OS support underway, and Qualcomm is stepping up to announce the first-ever mass-market RISC-V Android SoC.

RISC-V International warns about US interference in development

No different than other open technology standards like Ethernet

The chief executive of RISC-V International has warned that US efforts to corner the chip market under the guise of security could have a chilling effect on open standards and the development of better chips.

Qualcomm shows more interest in RISC-V

Arm should be worried

One of Arm's biggest customers Qualcomm is trying out RISC-V and getting involved in a joint venture dedicated to the architecture.

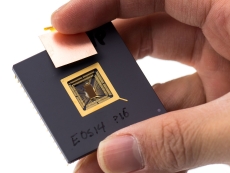

Chinese boffins create RISC-V CPU in five hours

AI is risky business

A group of Chinese scientists has published (PDF) a paper titled Pushing the Limits of Machine Design: Automated CPU Design with AI in which they tell the epic adventure of how they created a new industrial-scale RISC-V CPU in under five hours.

Samsung joins RISC-V Software Ecosystem

May the road Rise with you

Samsung Electronics has announced that it has joined RISE (RISC-V Software Ecosystem), an open-source software development project to build and develop an advanced semiconductor ecosystem.

PINE64 updates Star64 single-board computer

Gets a quad-core RISC-V processor

PINE64 has an update about their Star64 single-board computer with a quad-core RISC-V processor: it will be available on April 4th in two configurations: 4GB and 8GB LPDDR4 memory for $69.99 and $89.99.

Asus Tinker Board V is the first one with 64-bit RISC-V processor

1GHz Andes AX45MP single-core

Asus' Tinker Board lineup has been around for quite some time but now, we have the first one that will be using a RISC-V processor, the Asus Tinker V.

Intel kills off RISC-V developer environment

Can't find a way on Pathfinder

While the world+dog is looking closely at RISC-V, Chipzilla has killed off its open source RISC-V developer environment, Pathfinder.

HiFive Pro P550 development board ready for the summer

RISC-V business

SiFive and Intel have said that their HiFive Pro P550 development board is on track for release during summer.